Because we only want our state encoding to be visible to the module in which we will write the FSM, we will use the latter: localparam. local_name statement terminator ( ) grouping parenthesis, module instantiation, function and task call subscript, range as in // This is the main function that generates the VHDL and the Verilog corresponding to MyTopLevel.

The function split_using_delimiter_fn, parses through each Parametrized Verilog Modules. The type of a parameter (or a local parameter) is the type of whatever value is eventually assigned to it during elaboration. tmLanguage fileTypes sv SV foldingStartMarker (begin)\s*(//. Passing (parameter string "filename") to include statement in verilog I want to pass a filename from upper to lower verilog entity so that the lower entity can use it.

#Synplify pro tutorial software#

For example, to pass a binary string 1010 from a Block Design File to Verilog HDL, you cannot simply use the value 1001, because the Quartus ® Prime software interprets it as a decimal value. SystemVerilog also includes a number of special methods to work with strings. 2 Sandeep Vaniya's Advanced Use of define macro in SystemVerilog (not so advanced actually !!!) From reading these it might be apparent that define macro can be used for adding a postfix to the variable, but not prefix. Verilog has a feature allowing modules to be parametrized, meaning that properties of the module can be defined or overridden by the user of said modules. Before getting started with actual examples, here are a few notes on conventions.

#Synplify pro tutorial license#

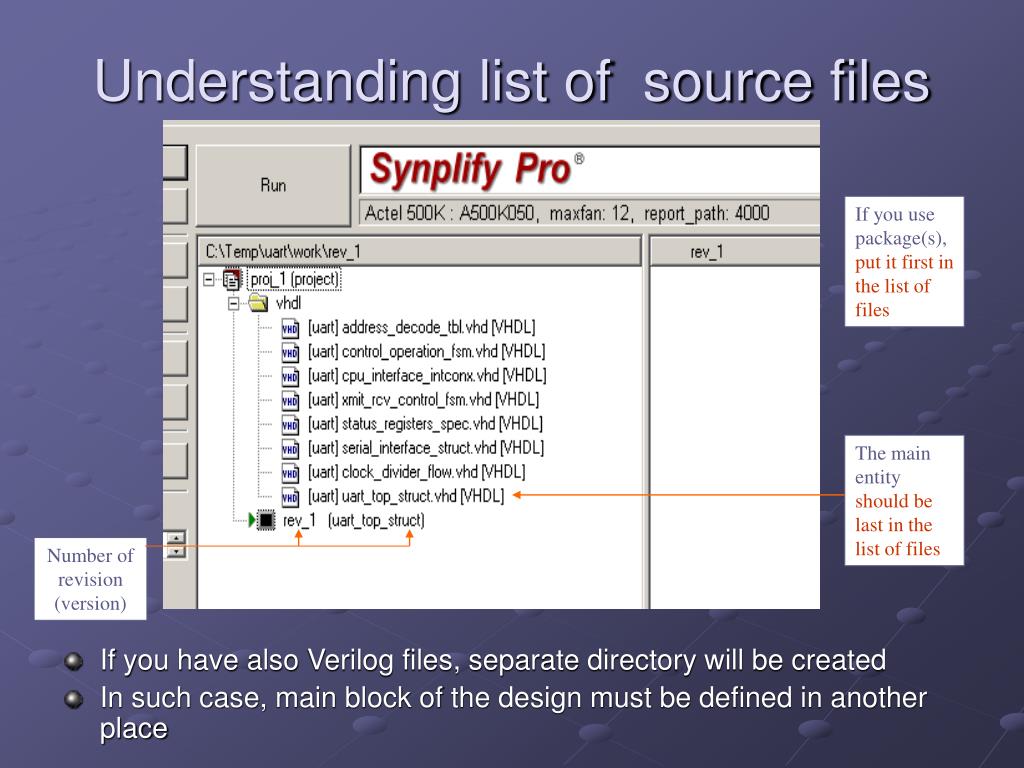

Synplify® Premier software provides all of the features of Synplify Pro as well as a comprehensive suite of tools for advanced FPGA design, see the Synplify Feature Comparison Chart.Org) COPYRIGHT AND LICENSE – SystemVerilog was designed to enhance both the design and verificationcapabilities of traditional Verilog Technically, there is no such thing as “Verilog” – the IEEE changed the name to “SystemVerilog” in 2009 VCS, Design Compiler and Synplify-Pro all support RTL modeling with SystemVerilog Verilog is a design language, and I am not sure about the system verilog concepts but in verilog if I write the parameter outside module( in a DUT), I get the errors as: 1.

#Synplify pro tutorial code#

Synplify Pro software uses a single, easy-to-use interface and has the ability to perform incremental synthesis and intuitive HDL code analysis.įor designers of large designs that need the fastest possible synthesis runtimes and the highest quality timing, area and power results. The software also supports FPGA architectures from a variety of FPGA vendors, including Altera, Achronix, Lattice, Microsemi and Xilinx, all from a single RTL and constraint source. Synplify software supports the latest VHDL and Verilog language constructs including SystemVerilog and VHDL-2008. Synplify Pro® FPGA synthesis software is the industry standard for producing high-performance and cost-effective FPGA designs.

0 kommentar(er)

0 kommentar(er)